Cân bằng nguồn xung - Switching mắc song song

Bài toán trình bày phương pháp cân bằng dòng cho nguồn switching mắc song song để đảm bảo các khối nguồn cơ sở có dòng điện đầu ra giống nhau. Bài báo đưa ra ví dụ cân bằng nguồn switching trên cơ sở kỹ thuật số sử dụng công nghệ FPGA cho 2 modules cơ sở loại 28.5V-40A.

Bạn đang xem tài liệu "Cân bằng nguồn xung - Switching mắc song song", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Cân bằng nguồn xung - Switching mắc song song

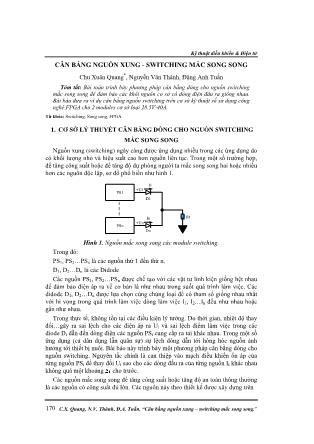

Kỹ thuật điều khiển & Điện tử C.X. Quang, N.V. Thành, Đ.A. Tuấn, “Cân bằng nguồn xung – switching mắc song song.” 170 CÂN BẰNG NGUỒN XUNG - SWITCHING MẮC SONG SONG Chu Xuân Quang*, Nguyễn Văn Thành, Đặng Anh Tuấn Tóm tắt: Bài toán trình bày phương pháp cân bằng dòng cho nguồn switching mắc song song để đảm bảo các khối nguồn cơ sở có dòng điện đầu ra giống nhau. Bài báo đưa ra ví dụ cân bằng nguồn switching trên cơ sở kỹ thuật số sử dụng công nghệ FPGA cho 2 modules cơ sở loại 28.5V-40A. Từ khóa: Switching, Song song, FPGA. 1. CƠ SỞ LÝ THUYẾT CÂN BẰNG DÒNG CHO NGUỒN SWITCHING MẮC SONG SONG Nguồn xung (switching) ngày càng được ứng dụng nhiều trong các ứng dụng do có khối lượng nhỏ và hiệu suất cao hơn nguồn liên tục. Trong một số trường hợp, để tăng công suất hoặc để tăng độ dự phòng người ta mắc song song hai hoặc nhiều hơn các nguồn độc lập, sơ đồ phổ biến như hình 1. PS1 PSn +U1 +Un D1 Dn I1 In Rt Hình 1. Nguồn mắc song song các module switching. Trong đó: PS1, PS2PSn là các nguồn thứ 1 đến thứ n. D1, D2Dn là các Didode Các nguồn PS1, PS2PSn được chế tạo với các vật tư linh kiện giống hệt nhau để đảm bảo điện áp ra về cơ bản là như nhau trong suốt quá trình làm việc. Các didode D1, D2Dn được lựa chọn cùng chủng loại để có tham số giống nhau nhất với hi vọng trong quá trình làm việc dòng làm việc I1, I2In đều như nhau hoặc gần như nhau. Trong thực tế, không tồn tại các điều kiện lý tưởng. Do thời gian, nhiệt độ thay đổigây ra sai lệch cho các điện áp ra Ui và sai lệch điểm làm việc trong các diode Di dẫn đến dòng điện các nguồn PSi cung cấp ra tải khác nhau. Trong một số ứng dụng (cả dân dụng lẫn quân sự) sự lệch dòng dẫn tới hòng hóc nguồn ảnh hưởng tới thiết bị nuôi. Bài báo này trình bày một phương pháp cân bằng dòng cho nguồn switching. Nguyên tắc chính là can thiệp vào mạch điều khiển ổn áp của từng nguồn PSi để thay đổi Ui sao cho các dòng đầu ra của từng nguồn II khác nhau không quá một khoảng cho trước. Các nguồn mắc song song để tăng công suất hoặc tăng độ an toàn thông thường là các nguồn có công suất đủ lớn. Các nguồn này theo thiết kế được xây dựng trên Thông tin khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số 46, 12 - 2016 171 nền tảng nguồn xung loại 1 theo phân loại của Nga như sơ đồ hình 2. K +E D L C + Ur Tải Hình 2. Sơ đồ nguồn xung loại 1. Theo sơ đồ khóa K đóng mở theo chu kỳ T, thời gian mở khóa (cho dòng chạy qua) Tx. TTx 2T t Ur E Hình 3. Chu kỳ đóng – mở của khóa K. Điện áp đầu ra tính theo công thức: Loại nguồn này thường dùng cho để làm cơ sở cho nguồn công suất lớn vì có chỉ số khối lượng - trọng lượng tốt nhất trong ba loại nguồn xung. Biến thể của loại nguồn này khi dùng với biến thế (Transformer) được mô tả trong hình 4. L K1 K2 K4 K3 +E C + Tải +U Hình 4. Nguồn loại một dùng với biến thế (Transformer). Điện áp ra: 2. TÍNH TOÁN XÂY DỰNG SƠ ĐỒ ĐIỀU KHIỂN CÂN BẰNG THEO PHƯƠNG PHÁP SỐ Phần điều khiển hầu hết các nguồn được thiết kế trên cơ sở IC TL494 hoặc tương đương. Việc can thiệp điều khiển được thực hiện bằng cách thay đổi điện áp so sánh chuẩn đưa vào đầu vào khuếch đại thuật toán để thay đổi điện áp ra sao cho Kỹ thuật điều khiển & Điện tử C.X. Quang, N.V. Thành, Đ.A. Tuấn, “Cân bằng nguồn xung – switching mắc song song.” 172 dòng cân bằng. Việc này được thực hiện bằng cách thay đổi điện áp bù qua mạch D/A sau xử lý. Ví dụ điển hình thiết kế điều khiển bằng cách thay đổi điện áp so sánh chuẩn trong nguồn dùng IC TL494 được thể hiện trên hình 5. Đây là mạch thiết kế Viện VLKT đã thiết kế nguồn switching phục vụ thiết bị quân sự gồm hai nguồn 28.5Vx40A mắc song song, phần mềm thực hiện đặt tham số sao cho dòng lệch không quá 5% Imax = 2A bằng cách thiết lập điện áp bù qua mạch chuyển đổi D/A tới chân DAC . Mạch bù điện áp trong sơ đồ mạch điện hình 5 chính là phần mạch đóng khung nét đứt. Hình 6 là mô hình nguyên lý chung của mạch bù điện áp. R13 27R R 1 5 2 K 7 R23 47K U2 TL431 R31 22K R 1 2 1 6 4 K C5 221 30 E2 Vref C11 122 19 E1 R29 33K R 1 1 6 8 K R20 3K9 R 1 7 4 7 0 R Q3 Dual Diode 1 2 3 A KK A R21 470K R22 3K3 R33 3K3 R25 27R VCC_494 Vref C4 104 R27 220R C6 2,2uF/16V DAC R30 7K5 C8 2.2uF/16V R 2 4 3 K 9 8 Vref R32 220R 1 R16 5K 2,3,6,7 R 1 0 6 8 K R28 3K3 +28.5V R26 100R +28.5V C7 22uF/16V C9 472 C10 221 U4 TL494I 12 71 2 1 6 15 8 11 3 4 1 3 9 10 5 1 4 6 VCC G N D IN 1 + IN1- IN 2 + IN2- C1 C2 C O M P DTC O C E1 E2 CT V R E F RT R18 330R R 1 4 7 5 K U3 HCPL0500 2 3 5 6 7 8 Hình 5. Sơ đồ mạch hiệu chỉnh điện áp 28,5V - 40A bằng phần mềm. + - DA R2 R3 Điện áp chuẩn (Uref) R1 Hình 6. Mạch bù điện áp. Như vậy, sơ đồ khối hệ thống nguồn mắc song song có xử lý cân bằng dòng được thể hiện như sau: ADC1 Cách ly FPGA DAC1 ADCn Cách ly DACn Sensor dòng khối nguồn 1 Sensor dòng khối nguồn n Khối nguồn 1 Khối nguồn n Hình 7. Sơ đồ khối hệ thống xử lý cân bằng. Lựa chọn bước thay đổi điện áp phù hợp với đặc tuyến VA của diode cách ly trong nguồn switching mắc song song. Thông tin khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số 46, 12 - 2016 173 Như bài báo đã đặt ra, sai số về dòng cho hai nguồn mắc song song không vượt quá ΔΙ, như vậy bước hiệu chỉnh điện áp đầu ra của nguồn PS phải nằm trong giới hạn sao cho mỗi khi thay đổi một bước (do hiệu chỉnh số) dòng đầu ra của nguồn được hiệu chỉnh nhỏ hơn ΔΙ. Xét đặc tuyến VA của hai loại diode công suất thông dụng được sử dụng cho mục đích này, chọn hai loại diode có dòng làm việc lớn hơn 50A, một là loại silic ký hiệu STTH60L06TV, một loại germany ký hiệu DSS2x121-0045B là hai loại tổ đề tài sử dụng cho nguồn công công suất mắc song song. Đặc tuyến VA của hai loại thể hiện trên hai hình 8, hình 9. Với diode Ge, đoạn dốc nhất của đặc tuyến (đoạn có sự thay đổi dòng nhiều nhất khi thay đổi 1mV điện áp trên diode) là 5mV/A. Tương tự như vậy đoạn dốc nhất của đặc tuyến với diode silic là 7.2mV/A. Độ lệch dòng phụ thuộc đặc tính – xem phụ lục kết quả đo thực tế. Với cùng điện áp, cùng chủng loại diode do đặc tính diode khác nhau mà dòng khác nhau (Bảng 1 – 6 trong phụ lục). Như vậy, để hệ thống làm việc bình thường với cả hai loại diode hiện có chúng ta lựa chọn bước thay đổi điện áp tương ứng với loại diode có sự thay đổi đặc tuyến cao hơn, tức là loại Ge, mỗi khi thay đổi dòng 1A, điện áp trên diode thay đổi 5mV. Như vậy, 5mV cũng là bước thay đổi điện áp trong mỗi chu kỳ phần mềm khi phát hiện có sự thay sai lệch dòng lớn hơn 2A giữa hai nguồn PS mắc song song. Hình 8. Đặc tuyến VA của diode STTH60L06TV (đại diện cho loại Si). Hình 9. Đặc tuyến VA của diode DSS2x121-0045B (đại diện cho loại Ge). 3. TÍNH TOÁN, VÀ XÂY DỰNG THUẬT TOÁN ĐIỀU KHIỂN CÂN BẰNG TRÊN FPGA Ứng dụng điều khiển cân bằng nguồn switching mắc song song trong thực tế, Viện VLKT đã thiết kế nguồn switching phục vụ thiết bị quân sự gồm 2 nguồn 28.5V x 40A mắc song song, phần mềm được đặt tham số sao cho dòng lệch không Kỹ thuật điều khiển & Điện tử C.X. Quang, N.V. Thành, Đ.A. Tuấn, “Cân bằng nguồn xung – switching mắc song song.” 174 quá 5% Imax = 2A, như sơ đồ trên hình 10. Với nguồn Switching, tần số làm việc trong khoảng 50kHz – 60kHz, thời gian giữa các lần hiệu chỉnh (thay đổi điện áp) được lấy lớn hơn thời gian quá độ của nguồn, 10ms là thời gian được nhóm tác giả lựa chọn vào thực tế. Tần số của nguồn do nhóm thực hiện là 50kHz, do đó, tốc độ lấy mẫu được chọn là 100kSps để lấy kết quả dòng trung bình không phụ thuộc vào sóng vân. Thuật toán điều khiển cân bằng 2 khối được thực hiện như trên hình 10. Như miêu tả trên hình 10, tín hiệu đưa tới từ bộ cảm biến hai khối nguồn được đưa đến bộ biến đổi ADC, bộ biến đổi ADC, và các mẫu được lấy liên tục cộng trung bình trong thời gian 10ms, như vậy, số mẫu cần lưu và lấy trung bình cho mỗi kênh khoảng 1000 mẫu. Tuy nhiên, do cấu trúc của FPGA nên số mẫu để lấy trung bình tương ứng cho mỗi kênh là 1024 mẫu. Sau khi lấy mẫu sẽ được thực hiện cộng trung bình thành mẫu dữ liệu trung bình đầu ra của mỗi kênh. Bắt đầu Lấy mẫu từ hai kênh ADC Tính toán trung bình các mẫu dữ liệu So sánh mức trung bình dữ liệu Vượt ngưỡng? 1 2 2 1 Tính toán lượng điều khiển cho hai kênh Tính toán lượng điều khiển DAC Điều khiển DAC đến từng khối 2 Hình 10. Lưu đồ thuật toán. Hai mẫu trung bình đầu ra từ bộ lấy trung bình được so sánh với nhau theo chu kỳ 10ms, nếu có sự sai khác giữa hai kênh tương ứng với sai số dòng ≥ 2A sẽ tiến hành điều chỉnh, mức điều chỉnh sai số hai kênh được bù theo chiều ưu tiên cho việc tăng dòng cho khối có dòng bé hơn, mỗi lần điều chỉnh tương ứng với 1A. Bộ biến đổi DAC thực hiện biến đổi tương ứng với mức điều chỉnh 1A cho mỗi lần điều chỉnh với chu kỳ 10ms, quá trình điều chỉnh được thực hiện cho đến khi hai Thông tin khoa học công nghệ Tạp chí Nghiên cứu KH&CN quân sự, Số 46, 12 - 2016 175 khối nguồn cân bằng. 4. ÁP DỤNG KẾT QUẢ Viện VLKT đã thiết kế chế tạo bộ nguồn công công suất gồm 2 nguồn 28,5Vx40A mắc song song, bộ nguồn đã được thử nghiệm tại đơn vị thay thế cho bộ nguồn đặc chủng trong một thiết bị quân sự có trong trang bị. Thử nghiệm cho thấy nguồn làm việc tin cậy, đúng như các tham số đã công bố trong bài báo. Nhóm nghiên cứu đã sử dụng bộ nguồn này đặt điện áp ban đầu cả hai bộ nguồn nội tại là 29V, với bước thay đổi một trong hai bộ nguồn là 10mV với một số loại tải khác nhau đề tài thử nghiệm với ba loại diode công suất: loại Ge, loại Silic và một loại đặc chủng của Nga, có đặc tuyến nằm giữa Si và Ge thông thường. Hình 11 chỉ ra đồ thị phân dòng cho một thử nghiệm bộ nguồn sử dụng phương pháp cộng dòng sử dụng diode của Nga khi có độ lệch điện áp giữa các bộ nguồn. 12 14 16 18 20 0 10 20 30 40 50 I1 (Dòng điện kênh 1) I2 (Dòng điện kênh 2) I Dòng điện trung bình Độ lệch điện áp 2 kênh ∆U (mV) C ư ờ ng độ d ò n g đ iệ n I (A ) Hình 11. Đồ thị phân dòng khi cộng dòng của hai khối nguồn. Chúng ta thấy rằng, với các diode khác nhau (kể cả diode kếp cùng chung một vỏ) ở các điểm làm việc khác nhau (dòng tải khác nhau) mặc dù điện áp đầu vào như nhau (29V) tải có thể cho dòng qua mỗi diode khác nhau, thậm chí khác nhau rất nhiều. Đây chính là lý do các bộ cộng công suất (2 module, 3 module) hay hỏng hóc. Việc thực hiện cân bằng dòng cho nguồn switching là việc làm cần thiết, đảm bảo cho nguồn làm việc an toàn, ổn định, lâu dài. Bộ điều khiển cân bằng dòng ngoài việc đảm bảo dòng các nhánh hội tụ theo dòng trung bình còn có tác dụng vô cùng quan trọng đó là ổn định và giảm đáng kể các trạng thái quá độ tại thời điểm cấp nguồn cho các tải làm giảm đáng kể tốc độ của toàn hệ thống. 5. KẾT LUẬN Việc thiết kế chế tạo khối nguồn switching mắc song song để cân bằng dòng là nhu cầu thực tế, với phần trình bày ở trên, cả lý thuyết và thực tế chứng minh là có thể làm được và có nhiều ứng dụng trong thực tế. Kỹ thuật điều khiển & Điện tử C.X. Quang, N.V. Thành, Đ.A. Tuấn, “Cân bằng nguồn xung – switching mắc song song.” 176 Bộ điều chỉnh cân bằng thực hiện việc kiểm tra sai số dòng điện giữa hai khối theo chu kỳ 10ms, đảm bảo điều chỉnh để độ lệch dòng trong hai khối nguồn không vượt quá 2A. Việc thực hiện cân bằng dòng cho nguồn switching là việc làm cần thiết, đảm bảo cho nguồn làm việc an toàn, ổn định, lâu dài. Bộ điều khiển cân bằng dòng ngoài việc đảm bảo dòng các nhánh hội tụ theo dòng trung bình còn có tác dụng vô cùng quan trọng đó là ổn định và giảm đáng kể các trạng thái quá độ tại thời điểm cấp nguồn cho các tải làm giảm đáng kể tốc độ của toàn hệ thống. TÀI LIỆU THAM KHẢO [1]. Ali, A., Z. Kai and K. Heikki “Modeling and control design of paralleled DC- DC switching converters”, Proceeding of the ICCCP’09, Feb, 2009. [2]. A. Testa, Fellow Member IEEE. R. Langella, Senior Member IEEE. “Switching Power Supplies: Analysis of Waveform Distortion”, Power & Enrgy Society, 2015. [3]. Bin Zhang, Hong Li, Xia Lei, “The Design of the Parallel Switching Power Supply System”, Research Juornal of Applied Sciences, October 10, 2013. [4]. Reason, John, “Solid-State Transfer Switch”: Electrical World, August, 1996 [5]. Yuxuan Sun, Xi Feng, “The Design and Implementation of Switching Power of High Power Factor in Communication Equipment”, Wuhan, China, Jan, 2015. ABSTRACT A METHOD TO REGULATE SWITCHING POWER SUPPLIES OPERATING IN PARALLEL One of the critical problems in regulating switching power supplies operating in parallel is to guarantee the stability and the reasonable similarity of output currents produced by the elementary power supply modules. The paper represents a method to regulate this type of switching power supply adopting digital FPGA-based technology for two module 28.5V – 40A. Keywords: Switching, Parallel, FPGA. Nhận bài ngày 01 tháng 06 năm 2016 Hoàn thiện ngày 26 tháng 09 năm 2016 Chấp nhận đăng ngày 14 tháng 12 năm 2016 Địa chỉ: Viện Vật lý Kỹ thuật, Viện KH&CNQS; *Email: [email protected].

File đính kèm:

can_bang_nguon_xung_switching_mac_song_song.pdf

can_bang_nguon_xung_switching_mac_song_song.pdf