Bài giảng Kỹ thuật số 2 - Chương 3: Các thiết bị logic lập trình

3. THIẾT KẾ MẠCH DNG PAL (Programmable Array Logic)

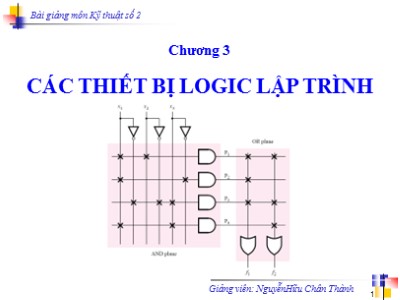

Cấu trúc của PAL tương tự như PLA nhưng chỉ có mảng AND lập trình được, mảng OR thì cố định.

- Ưu điểm:

Mảng OR nhanh hơn và nhỏ hơn

Giá thành giảm

Thường có sẵn các FF → các thiết kế mạch tuần tự.

- Khuyết điểm:

Chức năng bị hạn chế

Không thể dùng chung các số hạng tích.

Bạn đang xem 20 trang mẫu của tài liệu "Bài giảng Kỹ thuật số 2 - Chương 3: Các thiết bị logic lập trình", để tải tài liệu gốc về máy hãy click vào nút Download ở trên

Tóm tắt nội dung tài liệu: Bài giảng Kỹ thuật số 2 - Chương 3: Các thiết bị logic lập trình

Chương 3 CÁC THIẾT BỊ LOGIC LẬP TRÌNH Bài giảng môn Kỹ thuật số 2 1 Giảng viên: NguyễnHữu Chân Thành 1. GIỚI THIỆU Caùc choïn löïa cho vieäc thöïc hieän maïch: Bài giảng môn Kỹ thuật số 2 2 Giảng viên: NguyễnHữu Chân Thành 1. GIỚI THIỆU (tt) PLD laø teân goïi chung cho caùc vi maïch soá coù theå laäp trình ñeå cung caáp caùc chöùc naêng khaùc nhau. Moät PLD coù theå ñöôïc xem nhö moät “hoäp ñen” (black box). Hình 3.1 PLD nhö moät hoäp ñen. Bài giảng môn Kỹ thuật số 2 3 Giảng viên: NguyễnHữu Chân Thành 1. GIỚI THIỆU (tt) Hình 3.2 Moät caáu truùc laäp trình ñôn giaûn. Coù theå chia thaønh 3 hoï PLD chính: SPLD (Simple PLD), CPLD (Complex PLD) va ø FPGA (Field Programmable Gate Array). SPLD: ROM, PLA, PAL, GAL CPLD FPGA Bài giảng môn Kỹ thuật số 2 4 Giảng viên: NguyễnHữu Chân Thành 1. GIỚI THIỆU (tt) Caùc coâng ngheä laäp trình: Caàu chì (fusible link) Laøm ñöùt (noùng chaûy - blowing) caàu chì ñeå ngaét moät keát noái giöõa caùc ñöôøng. Chæ coù theå laäp trình moät laàn. Coù theå tích hôïp vôùi maät ñoä raát cao. Hình 3.3 Coâng ngheä caàu chì. Bài giảng môn Kỹ thuật số 2 5 Giảng viên: NguyễnHữu Chân Thành 1. GIỚI THIỆU (tt) Caàu chì nghòch (antifuse) Hình 3.4 Coâng ngheä caàu chì nghòch. Bài giảng môn Kỹ thuật số 2 6 Giảng viên: NguyễnHữu Chân Thành 1. GIỚI THIỆU (tt) Coâng ngheä EPROM-Based Caùc transistor nMOS ñöôïc duøng ñeå chuyeån maïch cho caùc keát noái giöõa caùc ñöôøng. Coù theå tích hôïp vôùi maät ñoä töông ñoái cao. Hình 3.5 Coâng ngheä EPROM-Based. a. PROM b. E PROM Bài giảng môn Kỹ thuật số 2 7 Giảng viên: NguyễnHữu Chân Thành 1. GIỚI THIỆU (tt) Coâng ngheä SRAM-Based Moät bit boä nhôù seõ ñieàu khieån moät phaàn töû chuyeån maïch. Coù theå laäp trình hay laäp trình laïi treân maïch (in-circuit programming). Khoâng giöõ thoâng tin khi taét nguoàn (volatile). Hình 3.6 Coâng ngheä SRAM-Based. Bài giảng môn Kỹ thuật số 2 8 Giảng viên: NguyễnHữu Chân Thành 2. THIẾT KẾ MẠCH DÙNG PLA (Programmable Logic Array) Bao goàm hai taàng coång logic: moät maûng coång AND laäp trình theo sau laø moät maûng coång OR laäp trình. Caùc thoâng soá: Soá ngoõ vaøo (n) Soá ngoõ ra (m) Soá haïng tích (k) Hình 3.7 Caáu truùc toång quaùt cuûa moät PLA. Bài giảng môn Kỹ thuật số 2 9 Giảng viên: NguyễnHữu Chân Thành 2. THIẾT KẾ MẠCH DÙNG PLA (tt) Ví duï 3.1: Hình 3.8 laø sô ñoà chi tieát cuûa moät PLA nhoû vôùi 3 ngoõ vaøo, 4 soá haïng tích vaø 2 ngoõ ra. Hình 3.8 Sô ñoà möùc coång cuûa 1 PLA. Hình 3.9 Sô ñoà nguyeân lyù cuûa PLA hình 3.8 Bài giảng môn Kỹ thuật số 2 10 Giảng viên: NguyễnHữu Chân Thành 2. THIẾT KẾ MẠCH DÙNG PLA (tt) Ngoaøi ra, cöïc tính ngoõ ra cuõng coù theå laäp trình baèng caùch noái theâm moät coång EX-OR vaøo moãi ngoõ ra. Hình 3.10 Caáu truùc cuûa PLA 4x8x4 vôùi cöïc tính ngoõ ra laäp trình ñöôïc. Bài giảng môn Kỹ thuật số 2 11 Giảng viên: NguyễnHữu Chân Thành 2. THIẾT KẾ MẠCH DÙNG PLA (tt) Ví duï 3.2 : Thöïc hieän maïch coäng ñuû duøng PLA 4x8x4 treân hình 3.10. Hình 3.11 Maïch coäng ñuû duøng PLA. Bài giảng môn Kỹ thuật số 2 12 Giảng viên: NguyễnHữu Chân Thành 2. THIẾT KẾ MẠCH DÙNG PLA (tt) Ví duï 3.3: Thöïc hieän haøm sau duøng PLA 4x8x4 treân hình 3.10: Hình 3.12 Maïch cho ví duï 3.3 Bài giảng môn Kỹ thuật số 2 13 Giảng viên: NguyễnHữu Chân Thành 2. THIẾT KẾ MẠCH DÙNG PLA (tt) Ví duï 3.3: (tt) Moät caùch khaùc ñeå thöïc hieän haøm treân laø ruùt goïn haøm tröôùc. Haøm sau khi ruùt goïn: Hình 3.13 Maïch daïng khaùc cho ví duï 3.3. Bài giảng môn Kỹ thuật số 2 14 Giảng viên: NguyễnHữu Chân Thành 2. THIẾT KẾ MẠCH DÙNG PLA (tt) Tröôøng hôïp thöïc hieän nhieàu haøm treân moät PLA coá gaéng duøng laïi caùc soá haïng tích truøng laëp caùc haøm coù theå ôû daïng khoâng toái giaûn. Ví duï 3.4: Xeùt boán haøm 4 bieán ñöôïc moâ taû ôû hình 3.14: Hình 3.14 Caùc haøm caàn thöïc hieän treân PLA. Bài giảng môn Kỹ thuật số 2 15 Giảng viên: NguyễnHữu Chân Thành 2. THIẾT KẾ MẠCH DÙNG PLA (tt) Ví duï 3.4: (tt) → caàn 14 soá haïng tích (cho caû 2 tröôøng hôïp) Hình 3.15 Laäp trình vôùi: (a) Caùc minterm; (b) Caùc thaønh phaàn ruùt goïn. Bài giảng môn Kỹ thuật số 2 16 Giảng viên: NguyễnHữu Chân Thành 2. THIẾT KẾ MẠCH DÙNG PLA (tt) Ví duï 3.4: (tt) Duøng chung caùc soá haïng tích truøng laëp : Hình 3.16 Phuû boán haøm vôùi 11 thaønh phaàn tích. Bài giảng môn Kỹ thuật số 2 17 Giảng viên: NguyễnHữu Chân Thành 2. THIẾT KẾ MẠCH DÙNG PLA (tt) Baøi taäp: Xaùc ñònh haøm F1 vaø F2 trong caøi ñaët PLA hình sau: Hình 3.17 Bài giảng môn Kỹ thuật số 2 18 Giảng viên: NguyễnHữu Chân Thành 2. THIẾT KẾ MẠCH DÙNG PLA (tt) Tröôøng hôïp thöïc hieän maïch tuaàn töï: duøng PLA thöïc hieän maïch logic toå hôïp traïng thaùi keá tieáp vaø ngoõ ra, keát hôïp vôùi caùc FF ñeå laøm caùc phaàn töû nhôù. Hình 3.18 Sô ñoà khoái thöïc hieän maïch tuaàn töï duøng PLA vaø D-FF. Bài giảng môn Kỹ thuật số 2 19 Giảng viên: NguyễnHữu Chân Thành 2. THIẾT KẾ MẠCH DÙNG PLA (tt) Ví duï 3.5: Thöïc hieän ASM cho ôû ví duï 2.4 duøng PLA vaø D-FF: Hình 3.19 Duøng caùc bieåu thöùc ñôn giaûn hoùa. Hình 3.20 Duøng tröïc tieáp caùc ñöôøng noái töø löu ñoà. Bài giảng môn Kỹ thuật số 2 20 Giảng viên: NguyễnHữu Chân Thành 3. THIẾT KẾ MẠCH DÙNG PAL (Programmable Array Logic) Caáu truùc cuûa PAL töông töï nhö PLA nhöng chæ coù maûng AND laäp trình ñöôïc, maûng OR thì coá ñònh. Öu ñieåm: Maûng OR nhanh hôn vaø nhoû hôn Giaù thaønh giaûm Thöôøng coù saün caùc FF → caùc thieát keá maïch tuaàn töï. Khuyeát ñieåm: Chöùc naêng bò haïn cheá Khoâng theå duøng chung caùc soá haïng tích. Bài giảng môn Kỹ thuật số 2 21 Giảng viên: NguyễnHữu Chân Thành 3. THIẾT KẾ MẠCH DÙNG PAL (tt) Ví duï 3.6: PAL vôùi 3 ngoõ vaøo, 2 ngoõ ra vaø 4 soá haïng tích nhö ôû hình 3.21 thöïc hieän caùc haøm sau: Hình 3.21 Thöïc hieän haøm vôùi PAL cuûa ví duï 3.6. Bài giảng môn Kỹ thuật số 2 22 Giảng viên: NguyễnHữu Chân Thành 3. THIẾT KẾ MẠCH DÙNG PAL (tt) Ví duï 3.7: Thöïc hieän caùc haøm sau duøng PAL ñöôïc cho treân hình 3.22a : Hình 3.22 Thöïc hieän haøm vôùi PAL cuûa ví duï 3.7. b) a) X X X Bài giảng môn Kỹ thuật số 2 23 Giảng viên: NguyễnHữu Chân Thành 3. THIẾT KẾ MẠCH DÙNG PAL (tt) Tröôøng hôïp duøng PAL thöïc hieän maïch tuaàn töï: töông töï PLA. Ví duï 3.8: Thöïc hieän maïch tuaàn töï Moore phaùt hieän chuoãi 101 duøng PAL vaø caùc D-FF: Hình 3.23 Thöïc hieän maïch tuaàn töï vôùi PAL vaø D-FF cuûa ví duï 3.8. Bài giảng môn Kỹ thuật số 2 24 Giảng viên: NguyễnHữu Chân Thành 3. THIẾT KẾ MẠCH DÙNG PAL (tt) Tröôøng hôïp duøng PAL thöïc hieän maïch tuaàn töï: töông töï PLA. Ví duï 3.8: Thöïc hieän maïch tuaàn töï Moore phaùt hieän chuoãi 101 duøng PAL vaø caùc D-FF: Hình 3.23 Thöïc hieän maïch tuaàn töï vôùi PAL vaø D-FF cuûa ví duï 3.8. Bài giảng môn Kỹ thuật số 2 25 Giảng viên: NguyễnHữu Chân Thành 3. THIẾT KẾ MẠCH DÙNG PAL (tt) Hình 3.24 Sô ñoà logic cuûa PAL 16L8. Giôùi thieäu moät soá loaïi PAL: Bài giảng môn Kỹ thuật số 2 26 Giảng viên: NguyễnHữu Chân Thành 3. THIẾT KẾ MẠCH DÙNG PAL (tt) Hình 3.25 Sô ñoà logic cuûa PAL 16R4. Bài giảng môn Kỹ thuật số 2 27 Giảng viên: NguyễnHữu Chân Thành 3. THIẾT KẾ MẠCH DÙNG PAL (tt) Hình 3.26 Sô ñoà logic cuûa PAL 16R6. Bài giảng môn Kỹ thuật số 2 28 Giảng viên: NguyễnHữu Chân Thành 3. THIẾT KẾ MẠCH DÙNG PAL (tt) Hình 3.27 Sô ñoà logic cuûa PAL 16R8. Bài giảng môn Kỹ thuật số 2 29 Giảng viên: NguyễnHữu Chân Thành 3. THIẾT KẾ MẠCH DÙNG GAL ( Generic Array Logic ) GAL: coù theâm caùc maïch phuï ôû sau ngoõ ra coång OR cho pheùp laäp trình vôùi caùc caáu hình khaùc nhau → macrocell . Hình 3.28 Caáu truùc tieâu bieåu cuûa moät macrocell. Bài giảng môn Kỹ thuật số 2 30 Giảng viên: NguyễnHữu Chân Thành 3. THIẾT KẾ MẠCH DÙNG GAL (tt) Hình 3.29 Sô ñoà logic cuûa GAL 16V8C (caáu hình “Complex”). Giôùi thieäu moät soá loaïi GAL: Bài giảng môn Kỹ thuật số 2 31 Giảng viên: NguyễnHữu Chân Thành 3. THIẾT KẾ MẠCH DÙNG GAL (tt) Hình 3.30 Sô ñoà logic cuûa GAL 16V8R (caáu hình “Registered”). Bài giảng môn Kỹ thuật số 2 32 Giảng viên: NguyễnHữu Chân Thành 3. THIẾT KẾ MẠCH DÙNG GAL (tt) Hình 3.31 Sô ñoà logic cuûa GAL 22V10. Bài giảng môn Kỹ thuật số 2 33 Giảng viên: NguyễnHữu Chân Thành 4. GIỚI THIỆU VỀ CPLD Moät CPLD goàm nhieàu khoái maïch treân 1 vi maïch ñôn vôùi caùc khoái noái daây beân trong keát noái caùc khoái maïch vôùi nhau. Moãi khoái maïch thöôøng coù caáu truùc töông töï PLA hay PAL. Hình 3.32 Caáu truùc cuûa moät CPLD. Bài giảng môn Kỹ thuật số 2 34 Giảng viên: NguyễnHữu Chân Thành 4. GIỚI THIỆU VỀ CPLD (tt) Hình 3.33 Caáu truùc moät phaàn cuûa CPLD. Bài giảng môn Kỹ thuật số 2 35 Giảng viên: NguyễnHữu Chân Thành 4. GIỚI THIỆU VỀ CPLD (tt) Hình 3.34a Caáu truùc CPLD Altera Max 7000 series. Giôùi thieäu moät soá loaïi CPLD LAB: Logic Array Blocks PIA : Programmable Interconnect Array Bài giảng môn Kỹ thuật số 2 36 Giảng viên: NguyễnHữu Chân Thành 4. GIỚI THIỆU VỀ CPLD (tt) Hình 3.34b Caáu truùc LAB cuûa Altera Max 7000 series. Giôùi thieäu moät soá loaïi CPLD Bài giảng môn Kỹ thuật số 2 37 Giảng viên: NguyễnHữu Chân Thành 4. GIỚI THIỆU VỀ CPLD (tt) Hình 3.34c Caáu truùc macrocell cuûa Altera Max 7000 series. Giôùi thieäu moät soá loaïi CPLD Bài giảng môn Kỹ thuật số 2 38 Giảng viên: NguyễnHữu Chân Thành 4. GIỚI THIỆU VỀ CPLD (tt) Hình 3.35a Caáu truùc CPLD Xilinx XC9500 series. Giôùi thieäu moät soá loaïi CPLD Bài giảng môn Kỹ thuật số 2 39 Giảng viên: NguyễnHữu Chân Thành 4. GIỚI THIỆU VỀ CPLD (tt) Hình 3.35b Caáu truùc khoái taïo haøm (FB) cuûa Xilinx XC9500. Giôùi thieäu moät soá loaïi CPLD Bài giảng môn Kỹ thuật số 2 40 Giảng viên: NguyễnHữu Chân Thành 4. GIỚI THIỆU VỀ CPLD (tt) Hình 3.35c Caáu truùc khoái phaân phoái soá haïng tích vaø macrocell cuûa Xilinx XC9500. Giôùi thieäu moät soá loaïi CPLD Bài giảng môn Kỹ thuật số 2 41 Giảng viên: NguyễnHữu Chân Thành 4. GIỚI THIỆU VỀ CPLD (tt) Hình 3.35d Caáu truùc khoái I/O cuûa Xilinx XC9500 series. Bài giảng môn Kỹ thuật số 2 42 Giảng viên: NguyễnHữu Chân Thành 5. GIỚI THIỆU VỀ FPGA FPGA khoâng chöùa caùc maûng AND vaø OR maø noù cung caáp caùc khoái logic khaû caáu hình CLB (Configurable Logic Block) ñeå caøi ñaët caùc haøm mong muoán. Hình 3.36 Caáu truùc toång quaùt cuûa moät FPGA. Bài giảng môn Kỹ thuật số 2 43 Giảng viên: NguyễnHữu Chân Thành 5. GIỚI THIỆU VỀ FPGA (tt) Moãi khoái logic trong FPGA tieâu bieåu coù moät soá ít caùc ngoõ vaøo vaø 1 ngoõ ra. Coù nhieàu loaïi khoái logic, loaïi thöôøng ñöôïc söû duïng nhieàu nhaát laø baûng tra LUT (lookup table) chöùa caùc oâ nhôù löu tröõ (storage cell) duøng ñeå caøi ñaët caùc haøm logic nhoû. Hình 3.37 LUT 2 ngoõ vaøo. Bài giảng môn Kỹ thuật số 2 44 Giảng viên: NguyễnHữu Chân Thành 5. GIỚI THIỆU VỀ FPGA (tt) Hình 3.38 LUT 3 ngoõ vaøo. Bài giảng môn Kỹ thuật số 2 45 Giảng viên: NguyễnHữu Chân Thành 5. GIỚI THIỆU VỀ FPGA (tt) Hình 3.39 Moät phaàn cuûa FPGA ñöôïc laäp trình. Bài giảng môn Kỹ thuật số 2 46 Giảng viên: NguyễnHữu Chân Thành 5. GIỚI THIỆU VỀ FPGA (tt) Hình 3.40a Caáu truùc khoái CLB cuûa Xilinx XC4000. Giôùi thieäu moät soá loaïi FPGA Bài giảng môn Kỹ thuật số 2 47 Giảng viên: NguyễnHữu Chân Thành 5. GIỚI THIỆU VỀ FPGA (tt) Hình 3.40b Caáu truùc khoái I/O cuûa Xilinx XC4000. Giôùi thieäu moät soá loaïi FPGA Bài giảng môn Kỹ thuật số 2 48 Giảng viên: NguyễnHữu Chân Thành 5. GIỚI THIỆU VỀ FPGA (tt) Hình 3.40c Caáu truùc khoái keát noái cuûa Xilinx XC4000. Bài giảng môn Kỹ thuật số 2 49 Giảng viên: NguyễnHữu Chân Thành 5. GIỚI THIỆU VỀ FPGA (tt) Hình 3.41a Caáu truùc cuûa FPGA Altera Flex 8000 series. Giôùi thieäu moät soá loaïi FPGA Bài giảng môn Kỹ thuật số 2 50 Giảng viên: NguyễnHữu Chân Thành 5. GIỚI THIỆU VỀ FPGA (tt) Hình 3.41b Caáu truùc khoái LAB vaø LE cuûa Altera Flex 8000 series. Giôùi thieäu moät soá loaïi FPGA Bài giảng môn Kỹ thuật số 2 51 Giảng viên: NguyễnHữu Chân Thành 6. THIẾT KẾ MẠCH DÙNG ROM Tham khaûo giaùo trình (trang 92-100). Bài giảng môn Kỹ thuật số 2 52 Giảng viên: NguyễnHữu Chân Thành Q&A Bài giảng môn Kỹ thuật số 2 53 Giảng viên: NguyễnHữu Chân Thành

File đính kèm:

bai_giang_ky_thuat_so_2_chuong_3_cac_thiet_bi_logic_lap_trin.ppt

bai_giang_ky_thuat_so_2_chuong_3_cac_thiet_bi_logic_lap_trin.ppt